Digital Library[ Search Result ]

Dual Write Buffer Algorithm for Improving Performance and Lifetime of SSDs

Se Jun Han, Dong Hyun Kang, Young Ik Eom

In this paper, we propose a hybrid write buffer architecture comprised of DRAM and NVRAM on SSD and a write buffer algorithm for the hybrid write buffer architecture. Unlike other write buffer algorithms, the proposed algorithm considers read pages as well as write pages to improve the performance of storage devices because most actual workloads are read-write mixed workloads. Through effectively managing NVRAM pages, the proposed algorithm extends the endurance of SSD by reducing the number of erase operations on NAND flash memory. Our experimental results show that our algorithm improved the buffer hit ratio by up to 116.51% and reduced the number of erase operations of NAND flash memory by up to 56.66%.

Improving Performance of I/O Virtualization Framework based on Multi-queue SSD

Tae Yong Kim, Dong Hyun Kang, Young Ik Eom

Virtualization has become one of the most helpful techniques in computing systems, and today it is prevalent in several computing environments including desktops, data-centers, and enterprises. However, since I/O layers are implemented to be oblivious to the I/O behaviors on virtual machines (VM), there still exists an I/O scalability issue in virtualized systems. In particular, when a multi-queue solid state drive (SSD) is used as a secondary storage, each system reveals a semantic gap that degrades the overall performance of the VM. This is due to two key problems, accelerated lock contentions and the I/O parallelism issue. In this paper, we propose a novel approach, including the design of virtual CPU (vCPU)-dedicated queues and I/O threads, which efficiently distributes the lock contentions and addresses the parallelism issue of Virtio-blk-data-plane in virtualized environments. Our approach is based on the above principle, which allocates a dedicated queue and an I/O thread for each vCPU to reduce the semantic gap. Our experimental results with various I/O traces clearly show that our design improves the I/O operations per second (IOPS) in virtualized environments by up to 155% over existing QEMU-based systems.

Hybrid Main Memory based Buffer Cache Scheme by Using Characteristics of Mobile Applications

Chansoo Oh, Dong Hyun Kang, Minho Lee, Young Ik Eom

Mobile devices employ buffer cache mechanisms, just as in computer systems such as desktops or servers, to mitigate the performance gap between main memory and secondary storage. However, DRAM has a problem in that it accelerates battery consumption by performing refresh operations periodically to maintain the stored data. In this paper, we propose a novel buffer cache scheme to increase the battery lifecycle in mobile devices based on a hybrid main memory architecture consisting of DRAM and non-volatile PCM. We also suggest a new buffer cache policy that allocates buffers based on process states to optimize the performance and endurance of PCM. In particular, our algorithm allocates each page to the appropriate position corresponding to the state of the application that owns the page, and tries to ensure a rapid response of foreground applications even with a small amount of DRAM memory. The experimental results indicate that the proposed scheme reduces the elapsed time of foreground applications by 58% on average and power consumption by 23% on average without negatively impacting the performance of background applications.

A Buffer Cache Replacement Algorithm for Considering both Hybrid Main Memory and Storage

PRAM is being considered as a potential successor to DRAM because of its characteristics such as byte-addressability, non-volatility, and high density. To gain its benefits, buffer cache replacement algorithm based on PRAM has been actively studied. However, most of the previous studies on buffer cache replacement algorithm limitedly exploit the byte-level performance of PRAM by focusing its limited lifetime and slower access latency compared to DRAM. In this paper, we propose a novel buffer cache replacement algorithm that fully considers the byte-level performance of PRAM and the performance of secondary storage. To take advantage of small size write on PRAM, proposed scheme keeps pages, which are frequently accessed with a small size write, on PRAM and allows the selective page migration from DRAM to PRAM. As a result, our scheme significantly reduces the number of PRAM writes. Our experimental results indicate for real workloads that our scheme reduces the number of PRAM writes by up to 92% and improves its performance by up to 62% compared to CLOCK.

SSD Caching for Improving Performance of Virtualized IoT Gateway

It is important to improve the performance of storage in the home cloud environment within the virtualized IoT gateway since the performance of applications deeply depends on storage. Though SSD caching is applied in order to improve the storage, it is only used for read-cache due to the limitations of SSD such as poor write performance and small write endurance. However, it isimportant to improve performance of the write operation in the home cloud server, in order to improve the end-user experience. This paper propose a novel SSD caching which considers write-data as well as read-data. We validate the enhancement in the performance of random-write by transforming it to the sequential patterns.

Data Consistency-Control Scheme Using a Rollback-Recovery Mechanism for Storage Class Memory

Hyun Ku Lee, Junghoon Kim, Dong Hyun Kang, Young Ik Eom

Storage Class Memory(SCM) has been considered as a next-generation storage device because it has positive advantages to be used both as a memory and storage. However, there are significant problems of data consistency in recently proposed file systems for SCM such as insufficient data consistency or excessive data consistency-control overhead. This paper proposes a novel data consistency-control scheme, which changes the write mode for log data depending on the modified data ratio in a block, using a rollback-recovery scheme instead of the Write Ahead Logging (WAL) scheme. The proposed scheme reduces the log data size and the synchronization cost for data consistency. In order to evaluate the proposed scheme, we implemented our scheme on a Linux 3.10.2- based system and measured its performance. The experimental results show that our scheme enhances the write throughput by 9 times on average when compared to the legacy data consistency control scheme.

Design and Implementation of Efficient Mitigation against Return-oriented Programming

Jeehong Kim, Inhyeok Kim, Changwoo Min, Young Ik Eom

An ROP attack creates gadget sequences which consist of existing code snippets in a program, and hijacks the control flow of a program by chaining and executing gadget sequences consecutively. Existing defense schemes have limitations in that they cause high execution overhead, an increase in the binary size overhead, and a low applicability. In this paper, we solve these problems by introducing zero-sum defender, which is a fast and space-efficient mitigation scheme against ROP attacks. We find a fundamental property of gadget execution in which control flow starts in the middle of a function without a call instruction and ends with a return instruction. So, we exploit this property by monitoring whether the execution is abused by ROP attacks. We achieve a very low runtime overhead with a very small increase in the binary size. In our experimental results, we verified that our defense scheme prevents real world ROP attacks, and we showed that there is only a 2% performance overhead and a 1% binary size increase overhead in several benchmarks.

Design and Implementation of a Dynamic Instrumentation Framework based on Light-weight Dynamic Binary Translation

Jeehong Kim, Dongwoo Lee, Inhyeok Kim, Young Ik Eom

Dynamic binary instrumentation is a code insertion technique for debugging a program without scattering its execution flow, while the program is running. Most dynamic instrumentations are implemented using dynamic binary translation techniques. Existing studies translated program codes dynamically by parsing the machine code stream to intermediate representation (IR) and then applying compilation techniques for IRs. However, they have high overhead during translation, which is a major cause of difficulty in applying the dynamic binary translation technique to the program which requires high responsiveness. In this paper, we introduce a light-weight dynamic binary instrumentation framework based on a novel dynamic binary translation technique which has low overhead while translating the program code. In order to reduce the translation overhead, our approach adopts a tabular-based address translation and exploits a translation bypassing scheme, which stores the translated address of a frequently called library function in advance. It then accesses the translated address and executes function codes without code translation when calling the function. Our experiment results demonstrated that the proposed approach outperforms the prior dynamic binary translation techniques from 2% up to 65%.

Para-virtualized Library for Bare-metal Network Performance in Virtualized Environment

Dongwoo Lee, Youngjoong Cho, Young Ik Eom

Now, virtualization is no more emerging research area, and we can easily find its application in our circumstance. Nevertheless, I/O workloads are reluctant to be applied in virtual environment since they still suffer from unacceptable performance degradation due to virtualization latency. Many previous papers identified that virtual I/O overhead is mainly caused by exits and redundant I/O stack, and proposed several techniques to reduce them. However, they still have some limitations. In this paper, we introduce a novel I/O virtualization framework which improves I/O performance by exploiting multicore architecture. We applied our framework to the virtual network, and it improves TCP throughput up to 169%, and decreases UDP latency up to 38% on the network with the 10Gbps NIC.

Search

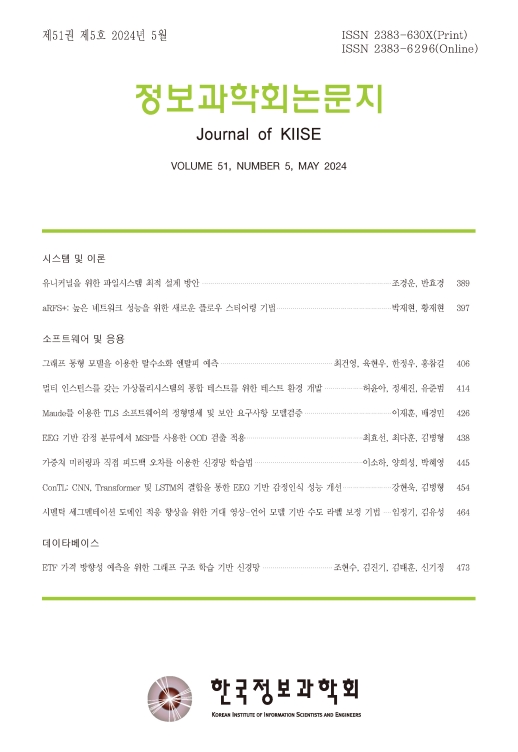

Journal of KIISE

- ISSN : 2383-630X(Print)

- ISSN : 2383-6296(Electronic)

- KCI Accredited Journal

Editorial Office

- Tel. +82-2-588-9240

- Fax. +82-2-521-1352

- E-mail. chwoo@kiise.or.kr