Digital Library[ Search Result ]

L2LRU: Learning-based Page Movement Policy for LRU Page Replacement Policy

http://doi.org/10.5626/JOK.2021.48.9.981

The LRU (least-recently used) page replacement policy has been designed to enhance the cache hit ratio by moving the page that is repeatedly accessed on the cache, to the head of the list. However, the LRU policy sometimes incurs a situation of system stall (or wait) because it requires lock-unlock commands to move each page. In this paper, we propose a new page replacement policy, called L2LRU(Learning-based Lock-free LRU), that determines whether to move or not a page by learning the reuse distance of the page with deep-learning techniques. Unlike LRU, L2LRU moves the page to the position with a high possibility of access in the near future. For evaluation, we implemented L2LRU based on trace-driven simulation and used Microsoft Research Cambridge Trace as the input of the simulation. The results clearly confirmed that L2LRU reduced the number of lock-unlock commands by up to 91% compared to the traditional LRU policy.

A Buffer Cache Replacement Algorithm for Considering both Hybrid Main Memory and Storage

PRAM is being considered as a potential successor to DRAM because of its characteristics such as byte-addressability, non-volatility, and high density. To gain its benefits, buffer cache replacement algorithm based on PRAM has been actively studied. However, most of the previous studies on buffer cache replacement algorithm limitedly exploit the byte-level performance of PRAM by focusing its limited lifetime and slower access latency compared to DRAM. In this paper, we propose a novel buffer cache replacement algorithm that fully considers the byte-level performance of PRAM and the performance of secondary storage. To take advantage of small size write on PRAM, proposed scheme keeps pages, which are frequently accessed with a small size write, on PRAM and allows the selective page migration from DRAM to PRAM. As a result, our scheme significantly reduces the number of PRAM writes. Our experimental results indicate for real workloads that our scheme reduces the number of PRAM writes by up to 92% and improves its performance by up to 62% compared to CLOCK.

Search

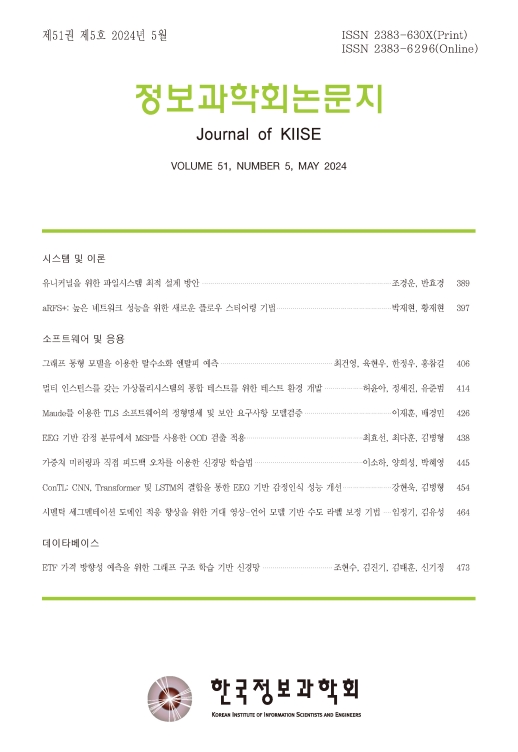

Journal of KIISE

- ISSN : 2383-630X(Print)

- ISSN : 2383-6296(Electronic)

- KCI Accredited Journal

Editorial Office

- Tel. +82-2-588-9240

- Fax. +82-2-521-1352

- E-mail. chwoo@kiise.or.kr