Digital Library[ Search Result ]

Study of Effective Valid Page Tracking Methods in Mobile Flash Storage without DRAM

http://doi.org/10.5626/JOK.2025.52.5.357

Mobile systems, commonly use flash-based storage devices like Universal Flash Storage (UFS). These devices are designed with a small form factor and operate under limited power and budget constraints, often lacking large internal DRAM. As a result, they rely on small SRAM to run the Flash Translation Layer (FTL). This limitation makes it difficult to manage metadata, such as address mapping tables and the Valid Page Bitmap related to garbage collection (GC), within SRAM. Managing the Valid Page Bitmap in flash memory poses challenges due to performance degradation from significant metadata I/O overhead. This paper proposes an efficient method for tracking valid pages within specific blocks by managing L2P segment bitmaps per block. This approach minimizes the metadata access overhead during valid page tracking, leading to improved performance. Evaluation results indicate up to an 83% reduction in latency for finding valid pages compared to existing methods, particularly with a 128KB I/O unit.

Sequentiality-Aware Hash-based FTL

Jaemin Shin, Ilbo Jeong, Li Xiaochang, Jihong Kim

http://doi.org/10.5626/JOK.2020.47.8.717

As the capacity of an SSD significantly increases, the SSD needs a larger DRAM for managing SSD-internal information. Since the cost of DRAM is an important factor in deciding the overall SSD price, it is important to reduce the DRAM cost without a performance degradation. In this paper, we propose a novel hash-based FTL mapping technique that meets this goal. Unlike an existing hash-based scheme, our technique introduces a virtual block scheme which enables to exploit the sequentiality of the logical address which effectively reduces the garbage collection overhead. Experimental results showed that SEQhFTL can reduce this overhead as much as PFTL while only maintaining 39% of PFTL’s metadata used on average.

A Cross Layer Optimization Technique for Improving Performance of MLC NAND Flash-Based Storages

Jisung Park, Sungjin Lee, Jihong Kim

http://doi.org/10.5626/JOK.2017.44.11.1130

The multi-leveling technique that stores multiple bits in a single memory cell has significantly improved the density of NAND flash memory along with shrinking processes. However, because of the side effects of the multi-leveling technique, the average write performance of MLC NAND flash memory is degraded more than twice that of SLC NAND flash memory. In this paper, we introduce existing cross-layer optimization techniques proposed to improve the performance of MLC NAND flash-based storages, and propose a new integration technique that overcomes the limitations of existing techniques by exploiting their complementarity. By fully exploiting the performance asymmetry in MLC NAND flash devices at the flash translation layer, the proposed technique can handle many write requests with the performance of SLC NAND flash devices, thus significantly improving the performance of NAND flash-based storages. Experimental results show that the proposed technique improves performance 39% on average over individual techniques.

Search

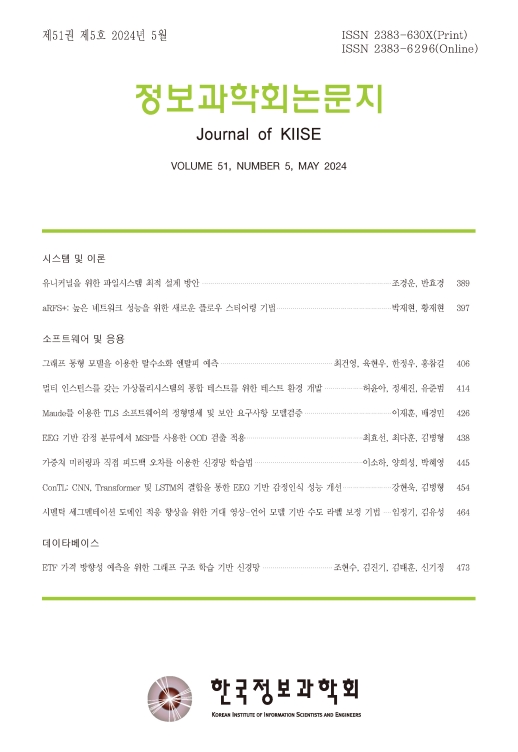

Journal of KIISE

- ISSN : 2383-630X(Print)

- ISSN : 2383-6296(Electronic)

- KCI Accredited Journal

Editorial Office

- Tel. +82-2-588-9240

- Fax. +82-2-521-1352

- E-mail. chwoo@kiise.or.kr