Digital Library[ Search Result ]

Improving the Performance and Usability of Server Systems through Dynamic Use of Persistent Memory

http://doi.org/10.5626/JOK.2021.48.10.1077

Persistent Memory (PM) has been studied assuming that it can only be used as main memory, storage, or storage cache. In this paper, we present HMMS (Hybrid Memory Management System), which is a memory management system that allows PM to play all these roles, not exclusively, but simultaneously. Specifically, HMMS dynamically and appropriately allocates these three roles by reflecting the state of the computing system and the users’ requests. With HMMS, we aim to improve the functionality and performance of computing systems where DRAM and PM coexist.

Efficient Process Checkpointing through Fine-Grained COW Management in New Memory based Systems

Jay H. Park, Young Je Moon, Sam H. Noh

We design and implement a process-based fault recovery system to increase the reliability of new memory based computer systems. A rollback point is made at every context switch to which a process can rollback to upon a fault. In this study, a clone process of the original process, which we refer to as a P-process (Persistent-process), is created as a rollback point. Such a design minimizes losses when a fault does occur. Specifically, first, execution loss can be minimized as rollback points are created only at context switches, which bounds the lost execution. Second, as we make use of the COW (Copy-On-Write)mechanism, only those parts of the process memory state that are modified (in page units) are copied decreasing the overhead for creating the P-process. Our experimental results show that the overhead is approximately 5% in 8 out of 11 PARSEC benchmark workloads when P-process is created at every context switch time. Even for workloads that result in considerable overhead, we show that this overhead can be reduced by increasing the P-process generation interval.

A Study of a Fast Booting Technique for a New memory+DRAM Hybrid Memory System

Hyeon Ho Song, Young Je Moon, Jae Hyeong Park, Sam H. Noh

Next generation memory technologies, which we denote as ‘new memory’, have both non-volatile and byte addressable properties. These characteristics are expected to bring changes to the conventional computer system structure. In this paper, we propose a fast boot technique for hybrid main memory architectures that have both new memory and DRAM. The key technique used for fast booting is write-tracking. Write-tracking is used to detect and manage modified data detection and involves setting the kernel region to read-only. This setting is used to trigger intentional faults upon modification requests. As the fault handler can detect the faulting address, write-tracking makes use of the address to manage the modified data. In particular, in our case, we make use of the MMU (Memory Management Unit) translation table. When a write occurs to the boot completed state, write-tracking preserves the original state of the modified address of the kernel region to a particular location, and execution continues. Upon booting, the fast booting process restores the preserved data to the original kernel region allowing rapid system boot-up. We develop the fast booting technique in an actual embedded board equipped with new memory. The boot time is reduced to less than half a second compared to around 15 seconds that is required for the original system.

I/O Translation Layer Technology for High-performance and Compatibility Using New Memory

Hyunsub Song, Young Je Moon, Sam H. Noh

The rapid advancement of computing technology has triggered the need for fast data I/O processing and high-performance storage technology. Next generation memory technology, which we refer to as new memory, is anticipated to be used for high-performance storage as they have excellent characteristics as a storage device with non-volatility and latency close to DRAM. This research proposes NTL (New memory Translation layer) as a technology to make use of new memory as storage. With the addition of NTL, conventional I/O is served with existing mature disk-based file systems providing compatibility, while new memory I/O is serviced through the NTL to take advantage of the byte-addressability feature of new memory. In this paper, we describe the design of NTL and provide experiment measurement results that show that our design will bring performance benefits.

Hybrid Main Memory Systems Using Next Generation Memories Based on their Access Characteristics

Recently, computer systems have encountered difficulties in making further progress due to the technical limitations of DRAM based main memory technologies. This has motivated the development of next generation memory technologies that have high density and non-volatility. However, these new memory technologies also have their own intrinsic limitations, making it difficult for them to currently be used as main memory. In order to overcome these problems, we propose a hybrid main memory system, namely HyMN, which utilizes the merits of next generation memory technologies by combining two types of memory: Write-Affable RAM(WAM) and Read-Affable RAM(ReAM). In so doing, we analyze the appropriate WAM size for HyMN, at which we can avoid the performance degradation. Further, we show that the execution time performance of HyMN, which provides an additional benefit of durability against unexpected blackouts, is almost comparable to legacy DRAM systems under normal operations.

Search

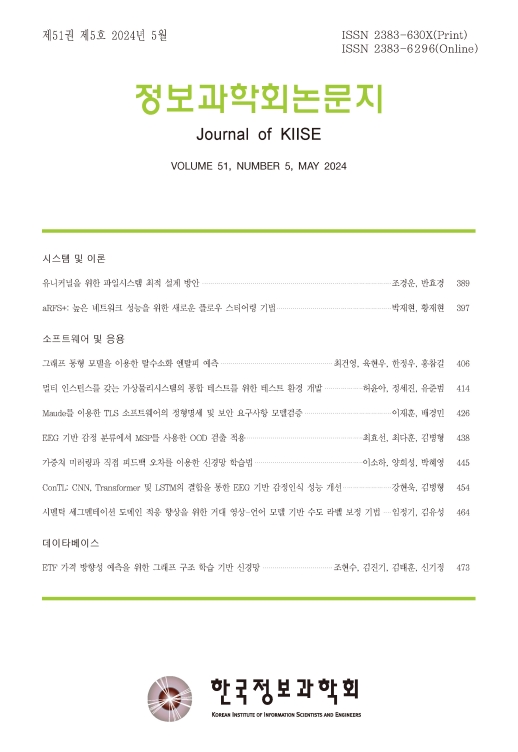

Journal of KIISE

- ISSN : 2383-630X(Print)

- ISSN : 2383-6296(Electronic)

- KCI Accredited Journal

Editorial Office

- Tel. +82-2-588-9240

- Fax. +82-2-521-1352

- E-mail. chwoo@kiise.or.kr